Brüel & Kjær has been helping the team at the Nanyang Technological University (NTU) in Singapore who have invented an ultra-high-quality chip that can tolerate more 'noise' from other components in a device. With reduced distortion, sound quality can be significantly improved.

Today, audio is about more than dynamic range or Total Harmonic Distortion (THD). It’s also about power: more of it for less. The team from the Division of Electrical and Electronics Engineering, part of NTU, are researching ultra-low-power, ultra-high-efficiency Class-D amplifiers (CDAs).

Ge Tong, a senior research scientist at NTU, began working with Brüel & Kjær 10 years ago when she was pursuing her PhD. “The project I was doing then was to design an active noise cancellation earphone (which was nascent at that time),” explains Ge Tong. “I used the Brüel & Kjær Head and Torso Simulator and also the PULSE system – and I am still using them now for my Class-D amplifier project and some other projects.”

Increasingly, devices need high-quality sound without sacrificing power efficiencies. For the majority of people, smartphones have become the main listening device, so audio quality is getting more attention from phone manufacturers. In view of the high power-efficiency requirement, it is not surprising that virtually all smart mobile devices today use a CDA as the driver to the primary loudspeaker.

However, Class-D audio applications require a wide breadth of design knowledge and technique. An ideal Class-D amplifying stage has no distortion and no noise generation in the audible band and provides close to 100% efficiency. However, in practice, CDAs have imperfections that generate distortion and noise.

A new CDA design

To still obtain high power efficiency, without resorting to a high switching frequency, the team at NTU proposed a novel CDA design. This new design embodies an input-modulated carrier generator and a phase-error-free, pulse-width modulation (PWM) modulator.

The prototype CDA features:

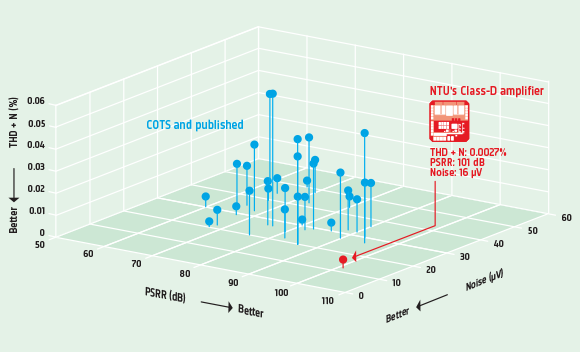

- A low Total Harmonic Distortion + Noise (THD + N) of 0.0027%

- The highest Power Supply Rejection Ratio (PSRR) to date, PSRR = 101 dB at 217 Hz

- A relatively low switching frequency, FSW ˜ 320 kHz at nominal operating conditions

CDAS: The Challenges

- The key parameters to qualify and quantify the performance of CDAs include:

- THD + N – measuring non-linearity and nois

- Power Supply Rejection Ratio (PSRR) – measuring immunity to supply nois

- Output noise – measuring noise level

- CDAs are largely deficient in fidelity and noise immunity. For example, only very few CDAs feature THD + N < 0.01% and a PSRR > 90 dB, and none feature PSRR > 100 dB

- A high switching frequency (FSW), for example FSW > 500 kHz, and/or complex multiple feedback loops can improve these parameters but can also incur undesirable compromises from:

CDAS can be classified into three categories

- High quality: THD + N < 0.02%, PSRR > 80 dB, and output noise < 40 µV

- Very-high quality: THD + N < 0.01%, PSRR > 90 dB, and output noise < 30 µV

- Ultra-high-quality: THD + N < 0.005%, PSRR > 100 dB, and output noise < 20 µV

Testing the design

Measuring CDA performance is relatively simple using an audio analyzer. Ge Tong and the NTU team measured THD + N and PSRR using a PULSE system that was seamlessly connected to a Head and Torso Simulator (HATS), which “listens” to the sound from a headset driven by a CDA, and measures the acoustical audio signal. Ge Tong explains: “This was essentially an integrated circuit design project. The development process started with the schematic design and simulation, followed by layout, parasitic extraction and post-layout simulations. If the post-layout simulations meet the design specifications, we can send the design for fabrication. Finally, the design is tested and verified. The whole process takes about one year.”

Too good to be true?

“The most challenging step in this project was probably to convince ourselves that it was in fact doable,” says Ge Tong. The design specifications are very stringent – far superior to anything that has been done before. On first appraisal, it might be thought that the specifications are too good to be realistic. The NTU team spent a lot of time rederiving the noise and non-linearity mechanisms and checking that their theoretical analyses were correct.

After a number of discussions and checks, everyone in the team was convinced that the design specifications could be achieved and the actual execution of the project went very smoothly, ultimately resulting in the team designing the first-ever ‘ultra-high-quality’ Class-D amplifier.

Brüel & Kjær’s Head and Torso Simulator is a manikin with mirrored external “ears” that ensures uniform and reliable binaural sound quality measurements. The calibrated ear simulators are optimized to measure all devices placed close to the ear, for example, hearing aids, hearing protectors, and headphones, as well as telephones and headsets.

Brüel & Kjær’s Head and Torso Simulator is a manikin with mirrored external “ears” that ensures uniform and reliable binaural sound quality measurements. The calibrated ear simulators are optimized to measure all devices placed close to the ear, for example, hearing aids, hearing protectors, and headphones, as well as telephones and headsets.

Head and Torso Simulator (HATS)

Brüel & Kjær’s Head and Torso Simulator is a manikin with mirrored external “ears” that ensures uniform and reliable binaural sound quality measurements. The calibrated ear simulators are optimized to measure all devices placed close to the ear, for example, hearing aids, hearing protectors, and headphones, as well as telephones and headsets.

Unprecedented audio performance

The result of this project is unprecedented performance from the CDA. The pinhead-sized chip encompassing the novel CDA design ultimately means that the audio from smartphones will sound like it is coming from high-end stereos, and wireless headphone users will be able to enjoy a longer battery life. Future applications of the chip include audio amplifiers, car audio systems, and televisions.

The team at NTU is continuing to improve the design and they aim to establish it as the industry gold standard for CDAs. Ge Tong concludes, “We hope to commercialize our CDAs in the near future. Several major IC design companies have expressed an interest in our design and our discussions with them are ongoing.”

Integrated Circuit (IC) Design

IC design involves the particular logic and techniques required to design ICs. In an IC, the multiple individual components (for example, transistors, diodes, resistors, capacitors, and the conductive pathways that connect all the components) are embedded directly into a single piece of silicon crystal.

- Simulation – pre-layout simulation is done to develop design constraints

- Post-layout simulation – simulation using the completed IC layout to verify compliance with the design constraints

- Parasitic effects – the unavoidable and usually unwanted capacitance that exists between the parts of an IC simply because of their proximity to each other

- Parasitic extraction – involves calculating the parasitic effects in the devices and interconnects of an IC

Dr Ge Tong

Dr Ge Tong is a multi-disciplinary engineer with research encompassing ultra-low-power, ultra-high-efficiency analogue circuits and signal processing, and printed/organic electronics on flexible substrates for biomedical and IoT applications. She has published ~40 research papers in top peer-reviewed journals and conference proceedings and filed 18 patents. She currently leads a research team of six researchers, and is the Co-principal Investigator of a research grant amounting to $600k from Singapore-MIT Alliance for Research and Technology. She is an Associate Editor of the IEEE Transaction on Circuits and Systems-II.

Abonnez-vous à notre Newsletter et recevez les dernières actualités en acoustique et vibrations